Digital Verilog Simulation

Verilog Simulation

VHDL Simulation

Today the most widely used language to describe electronics circuits and device models is the Spice netlist format (1973). However the Spice netlists are often hard to read and understand, and they lack a lot of the functionalities of programming languages which engineers would need while creating models and simulation.

The relatively new Verilog-A language (1995) provides an alternative method with an easy to read programming language style C like syntax. Thus Verilog-A is a suitable successor of the SPICE netlists for describing circuit topologies.

An even more sophisticated method of describing electronics circuit, containing both analog and digital components is the Verilog-AMS language. As we observed earlier, Verilog-AMS is a derivative of of the purely digital Verilog extended with the purely analog Verilog A and an interface for the connection of the analog and digital parts.

Most of the device libraries of TINA are in Spice netlist format. However you can already create and import models and place TINA macros in Verilog-A and Verilog-AMS format. You can find several language examples, device models, and circuits in the Examples\Verilog A folder of TINA

Verilog-AMS exmple:

The following circuit contains a Digital Analog Converter (DAC) macro with Serial Peripheral Interface (SPI) and a test bench macro, generating the digital SPI signal.The DAC model is defined in Verilog AMS. Interestingly, test bench on the left side is written in VHDL which is an example of mixing different HDLs but here we will concentrate on the Verilog AMS macro on the right. This circuit (DAC VAMS.TSC) is included in the EXAMPLES\Verilog AMS folder of TINA.

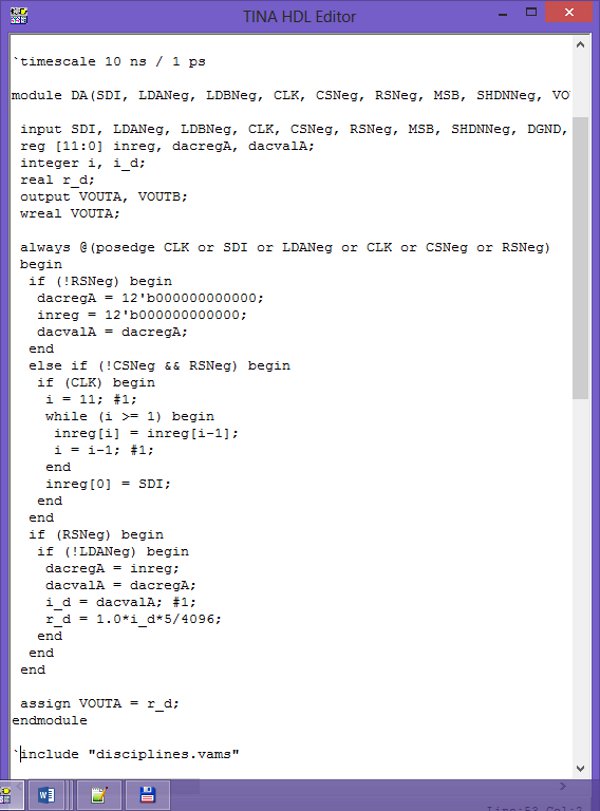

In TINA you can see the Verilog AMS code of the DAC model if you double-click the DAC macro and press the Enter Macro button. A part of the code is shown below.

We will not go into a detailed analysis of the code. We just want to show that in the first part shown above, the DA Verilog module converts the serial signal into an analog signal (VOUTA).

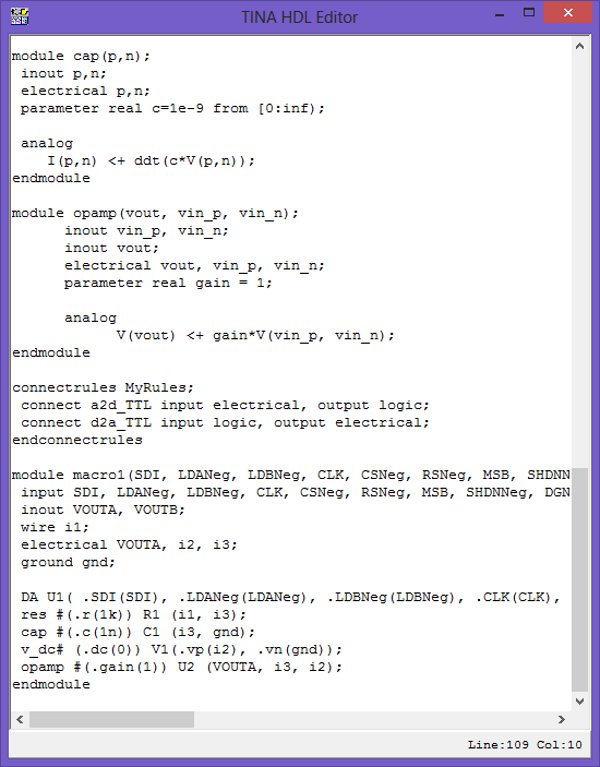

At the end of the macro shown below (in TINA you can scroll down there), the DA module is called and the signal is smoothed by a simple opamp and an RC filter using Verilog A instructions. You can also see the definition of the capacitor in the code fragment below.