数字VHDL仿真

VHDL(VHSIC超高速集成电路硬件描述语言)是IEEE标准硬件描述语言,电子设计师主要将其用芯片系统生产前所需的描述和仿真中。

现在,TINA 第7版及之后版本包含强大的数字VHDL仿真引擎。可以在TINA中将任意数字电路自动转化为VHDL代码并作为VHDL设计进行分析。此外,你可以分析大量的VHDL硬件,并使用VHDL自定义数字元件和硬件。VHDL的优越性不仅仅是IEEE标准,还体现在可在可编程器件如FPGA和CPLD中自动实现。

如果勾选了“分析/选项”中的“产生可综合代码”复选框,TINA可以产生可综合的VHDL代码以及相关的UCF文件。你可以使用T&M菜单中的“创建VHD和UCF文件”命令来保存新建的VHD和UCF文件。你可以使用Xilinx的免费工具Webpack来读取这些文件,产生描述设计实施细节的位流文件并将其烧入Xilinx FPGA芯片中。

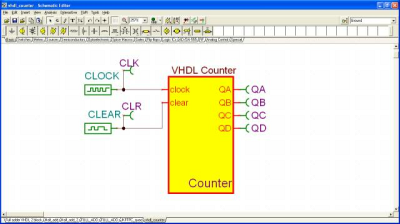

例如:以下电路为VHDL描述的计数器。

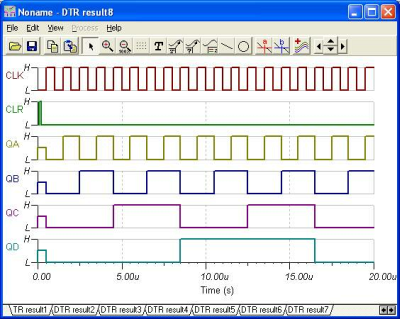

运行“分析/数字VHDL仿真”,给出以下图表:

如果在TINA中双击计数器块并按下“进入宏”,你可以看到定义计数器的VHDL代码。

library ieee; use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;----------------------------------------------------

ENTITY counter is port( clock: in std_logic; clear: in std_logic; QA, QB, QC, QD: out std_logic); END counter;

----------------------------------------------------

ARCHITECTURE behv of counter is

signal Pre_Q: unsigned( 3 downto 0 );BEGIN

-- behavioral description of the counter

process(clock, clear) begin

if clear = '1' then Pre_Q <= "0000"; elsif (clock='1' and clock'event) then

QA <= Pre_Q(0); QB <= Pre_Q(1); QC <= Pre_Q(2); QD <= Pre_Q(3);

Pre_Q <= Pre_Q + 1; end if; end process;END behv;

你可以在TINA中修改VHDL代码并立即看到效果。

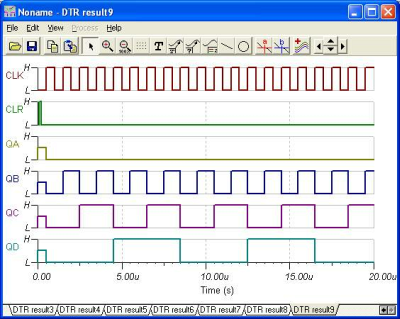

将Pre_Q <= Pre_Q + 1; 改为Pre_Q <= Pre_Q + 2; 并关闭对话框。

现在“分析/数字VHDL仿真”,给出以下图表:

你还可以在TINA的 交互模式中研究该电路。