Analyser un circuit numérique en utilisant la simulation numérique VHDL

VHDL (Virtual Hardware Description Language) est un langage stan- dard IEEE pour la description des matériels, qui est utilisé par les concepteurs électroniciens pour décrire et simuler leurs puces et systemes avant la fabrication.

TINA v7 et ses versions plus récentes comprennent désormais un puissant moteur de simulation VHDL numérique. Tout circuit numérique peut désormais etre converti automatiquement en un code VHDL sous TINA et analysé comme un schéma VHDL. En plus, vous pouvez analyser une large gamme de matériels disponibles dans VHDL et définir vos composants et matériels numériques dans VHDL. Le grand avantage de VHDL n’est pas seulement le fait qu’il est un langage standard IEEE pour la description des matériels, mais aussi qu’il peut etre réalisé automatiquement dans les dispositifs logiques programmables tels que les FPGA (les réseaux de portes programmables) et les CPLD (les circuits logiques programmables com- plexes).

TINA est a mesure de générer un code VHDL synthétisable meme temps que le fichier UCF correspondant si la case Generate synthesizable code [Générer un code synthétisable] est cochée dans le menu Analy- sis/Options [Analyse/Options]. Vous pouvez mémoriser les fichiers VHD et UCF créés en utilisant la commande «Create VHD & UCF File» [Créer un fichier VHD & UCF] dans le menu T&M. Vous pouvez lire les fichiers avec le Webpack gratuit de Xilinx et générer le fichier de train de bits décrivant l’implémentation de du schéma, puis téléchargez-le vers les puces FPGA de Xilinx.

Pour effectuer notre premiere analyse VHDL, chargez le circuit FULL_ADD.TSC a partir du dossier des exemples EXAMPLES/ VHDL de TINA. Le circuit suivant s’affiche :

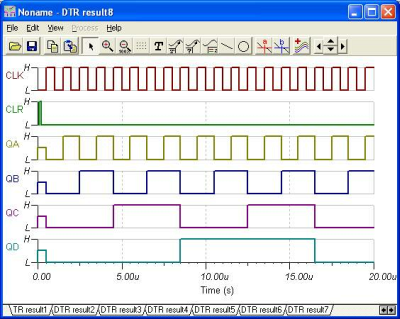

Running Analysis / Digital VHDL simulation, gives the following diagram:

If you double-click on the Counter block in TINA and press the Enter Macro button you can see the VHDL code defining the Counter.

library ieee; use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;----------------------------------------------------

ENTITY counter is port( clock: in std_logic; clear: in std_logic; QA, QB, QC, QD: out std_logic); END counter;

----------------------------------------------------

ARCHITECTURE behv of counter is

signal Pre_Q: unsigned( 3 downto 0 );BEGIN

-- behavioral description of the counter

process(clock, clear) begin

if clear = '1' then Pre_Q <= "0000"; elsif (clock='1' and clock'event) then

QA <= Pre_Q(0); QB <= Pre_Q(1); QC <= Pre_Q(2); QD <= Pre_Q(3);

Pre_Q <= Pre_Q + 1; end if; end process;END behv;

In TINA you can change the VHDL code and see the effect immediately.

Change the line Pre_Q <= Pre_Q + 1; above to Pre_Q <= Pre_Q + 2; and close the dialog.

Now Analysis / Digital VHDL simulation yields the following diagram–

You can also study this circuit in TINA's Interactive Mode.